Projects

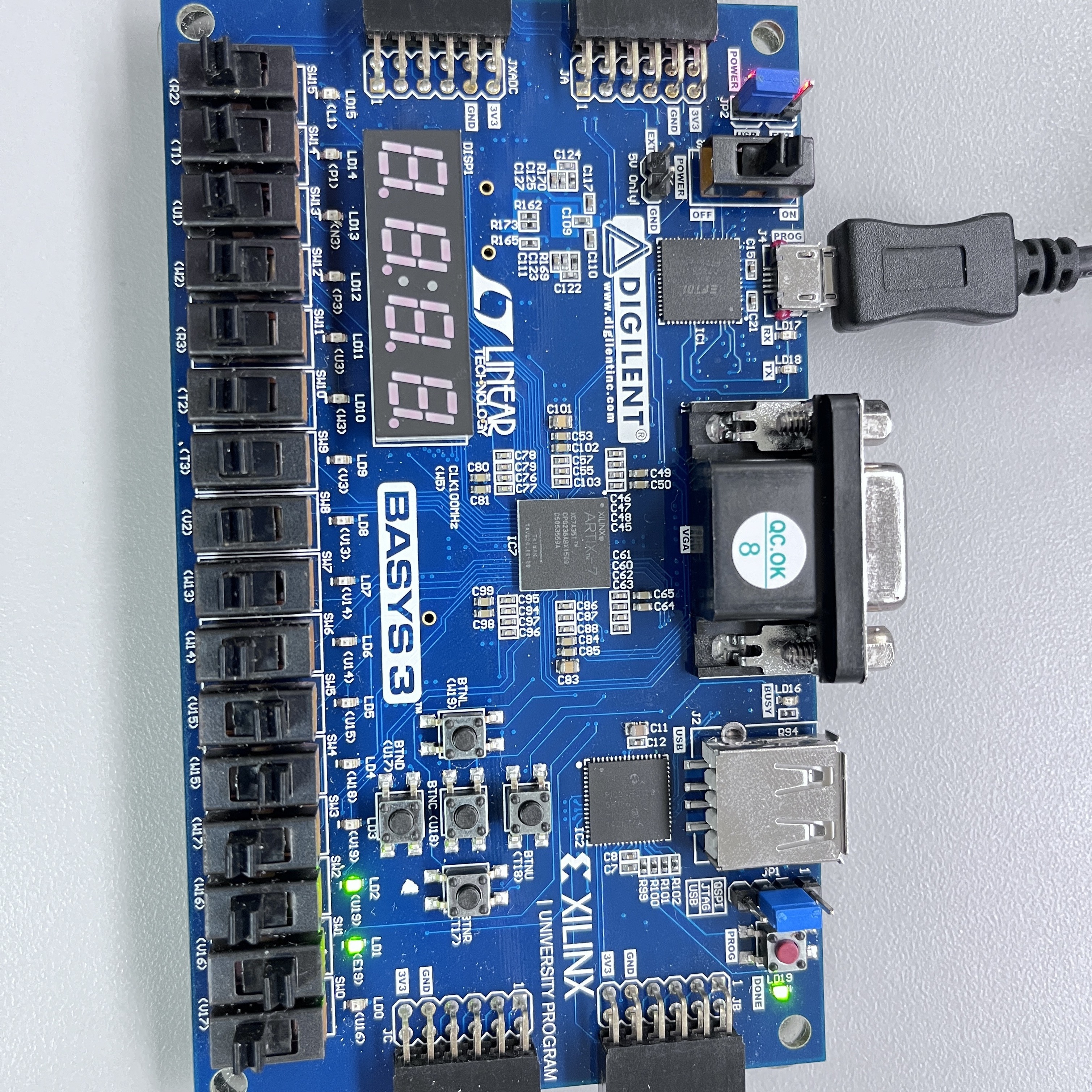

Synthesizing and deploying SystemVerilog designs onto a Basys 3 with Vivado 2024-11

A decoder, sequential circuit and ALU circuit were written in SystemVerilog and deployed in Basys 3 using Vivado

SystemVerilog, Hardware Engineering, Digital Design, FPGA

Read More

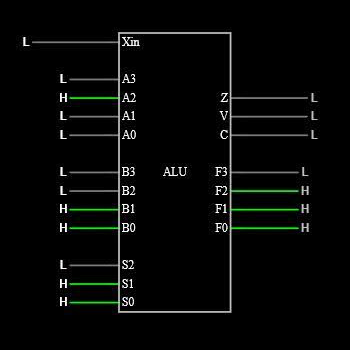

4-Bit ALU 2023-12

A 4-bit arithmetic logic unit (ALU) that performs eight basic operations was designed using Falstad and EDA Playground as the final project for my intro to digital design class.

SystemVerilog Digital Circuits Design Hardware Engineering

Read More

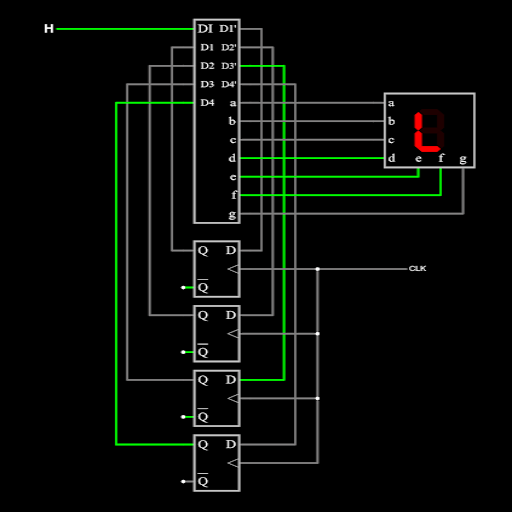

Scrolling Door Sign 2023-11

A finite state machine was designed to build a circuit for a scrolling door sign that displayed 'ALOHA' when an office is open, and 'PAU' when it is closed with custom logic.

SystemVerilog Digital Circuits Design Hardware Engineering

Read More

Connect Four 2021-12

A simulation of the real game 'Connect 4' was programmed as the final project in EE 160.

C Software Engineering Game

Read More